在传统的控制系统中,人们经常使用单片机作为控制核心。但是,该方法的硬件连接复杂且可靠性差,并且单片机的端口,内部定时器和中断源的数量受到限制。

在实际应用中,通常需要外部扩展芯片。这无疑给系统的设计带来很多不便。

现在,许多系统都使用可编程逻辑器件CPLD作为控制核心。与传统设计相比,它不仅简化了界面和控制,提高了系统的整体性能和工作可靠性,而且为系统集成创造了条件。

但是可编程逻辑器件的D触发器资源非常有限,可编程逻辑器件在控制时序方面不如微控制器那么方便。许多不熟悉的用户经常发现很难申请。

由可编程逻辑器件和单片机组成的双向通信控制器克服了两者的缺点,并最大限度地发挥了两者的优势。 1 CPLD与MCU AT89C51的双向串行通信原理1.1单片机至可编程逻辑器件的串行通信单片机至CPLD的串行通信接口电路是使用VHDL语言在CPLD中设计串行输入和并行输出8位移位寄存器,其端口与单片机的P1.4〜P1.7连接,如图1所示。

CS为单片机选择信号。当它为低时,使能8位寄存器。

当DCLOCK信号的上升沿到达clk端口时,8位移位寄存器将单片机输出的数据移位一位到cxin。当单片机A寄存器时当将A中的八位数据传输到CPLD时,在P1.6处将产生八个连续的上升沿,并且微控制器将A中的数据依次移至cxin。

八次之后,A中的数据段将出现在CPLD中。 Cxout。

VHDL源程序如下:•实体存储端口(clk,cxin,cs:in std_logic; cxout:out std_logic_vector(7降至0));结尾;建筑0;建筑0;临时变量并行输出开始处理(clk)开始(if(cs =& lsquo; 0& rsquo;))然后然后shift& lt; ==(others =& ls" lsamp; 0& rsquo;);如果未选择,则输出所有零lselsif(clk& quo; event clk =& rsquo; 1& lsquo;),然后输出;如果上升沿达到clk,则将其选中。 shift(7降低到1)< = shift(6降低到0);将八位数据向前移位一位(0)< = cxin;最低位由cxin端输入,如果;结束过程; cxout& lt; = shift;位变量发送到端口rtl;相应的微控制器控制子程序如下(要发送的数据存储在A中):CS EQU P1.4 EN EQU P1.5 DCLOCK EQU P1.6 DOUT EQU P1.7 CONV:PUSH 07H MOV R7,#8;将移位编号8存储在R7 CLR DCLOCK SETB CS中;选择移位寄存器CLR EN CLR C JXL:RLC A;向左移动一位,然后将要发送的数据发送到CY,C;发送到端口ACALL YS1MS SETB DCLOCK;给一个上升沿,将数据移入移位寄存器ACALL YS1MS CLR DCLOCK DJNZ R7,JXL;如果尚未达到8次,请发送下一个SETB EN;移动所有八位命令字,使EN上升沿以使CPLD执行相应的操作ACALL YS1MS POP 07H RET。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: tao@jepsun.com

产品经理: 陆经理

QQ: 2065372476

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

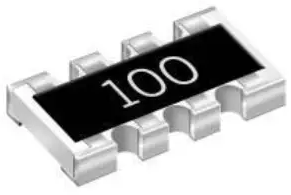

- 精密排阻与精密电阻品牌排行榜:2024年行业权威推荐 精密排阻与精密电阻品牌排行榜:2024年行业权威推荐在电子元器件领域,精密排阻和精密电阻因其高精度、稳定性强、温度系数低等特性,广泛应用于高端测量仪器、医疗设备、工业自动化及通信系统中。随着技术不断进步,市...

- 精密排阻与精密电阻品牌排行:2024年行业权威榜单解析 引言:精密电子元件的重要性在现代电子系统设计中,精密排阻(Precision Resistor Network)和精密电阻(Precision Resistor)是实现高精度信号调理、电压分压、电流检测等关键功能的核心元器件。随着工业自动化、医疗设备、高端测试...

- 精密电阻品牌排行 一个好的精密电阻,必须具备 老化小、温飘小、偏差小的特点,同时最好具备 可靠性高、功率余量大温升小、噪音低、串联电感分布电容小、电压系数小、焊接、振动及拉伸不容易变化等。当然,与基准相关的最重...

- HELI2品牌SMD-1.6X0.8mm LED灯珠:品质保障与技术创新的典范 HELI2品牌灯珠的市场定位与技术亮点HELI2作为专注于微型LED器件研发的品牌,其推出的SMD-1.6X0.8mm LED灯珠凭借出色的光电性能与稳定的制造工艺,在行业内赢得良好口碑。该系列产品不仅满足国际认证标准,更在一致性、寿命和色...

- 0402贴片电感品牌排行 1TDK成立于1935年日本,世界知名电子工业品牌,电子原材料及电子元器件领先企业,其产品广泛应用于信息、通讯、家用电器以及消费新电子产品。TDK在世界上30多个国家设立了200多个工厂、研发基地、营业网点,主要从事被动元...

- 汽车音响法拉电容的作用 如果汽车音响中出现了法拉级电容器的话,那么它的作用就像一个可充电的锂电池(或铅蓄电池)那样,在外部电源(包括汽车电源)供电时,音响可以工作,而且使供电电压更趋平稳;而当在一段时间内外部电源停止供电时,...

- 2.4G/WiFi/蓝牙双极天线与2.4GHz电阻在无线通信模块中的关键作用解析 2.4G/WiFi/蓝牙双极天线与2.4GHz电阻的技术协同机制在现代无线通信设备中,2.4G/WiFi/蓝牙双极天线作为核心组件,承担着信号发射与接收的重要任务。其设计需兼顾多频段兼容性与空间效率,尤其在智能家居、可穿戴设备和工业物联...

- 2.4G/WiFi/蓝牙双极天线与蓝牙5.2双模芯片:智能设备通信新引擎 引言:无线连接技术的演进随着物联网(IoT)和智能终端设备的普及,对高效、稳定、低功耗的无线通信方案需求日益增长。2.4G/WiFi/蓝牙双极天线配合蓝牙5.2与Wi-Fi双模芯片,正成为新一代智能设备的核心通信组件。一、双极天...

- G.G吊挂式2孔单排防水按钮台P02D1:可靠的选择 G.G吊挂式2孔单排防水按钮台P02D1是一款专为需要在潮湿或易受水溅环境中操作设备而设计的产品。这款按钮台采用高质量的防水材料制成,确保了即使在恶劣环境下也能正常工作。其设计简洁实用,安装方式简便快捷,通过吊挂...

- 汽车级厚膜排阻在新能源汽车中的关键应用与选型指南 汽车级厚膜排阻在新能源汽车中的核心作用在电动汽车与混合动力汽车中,电力电子控制单元(如BMS、DC-DC转换器、逆变器)对电路稳定性与信号完整性要求极高。汽车级厚膜排阻凭借其优异的电气性能与环境适应性,成为这些系...

- HELI2直角LED灯珠2.1X0.6mm与SMD-2.0X1.2mm LED灯珠性能对比及应用场景解析 HELI2直角LED灯珠2.1X0.6mm与SMD-2.0X1.2mm灯珠核心参数对比在现代电子设备中,LED灯珠作为关键的发光元件,其尺寸、封装形式和电气特性直接影响产品的设计灵活性与能效表现。本文将深入分析两款主流微型LED灯珠:HELI2直角型2.1X0.6...

- 如何正确选型与应用2.1X0.6mm直角LED灯珠与2.0X1.2mm SMD LED灯珠? 精准选型指南:2.1X0.6mm与2.0X1.2mm LED灯珠深度解析在电子产品开发过程中,选择合适的LED灯珠是确保产品可靠性与用户体验的关键环节。本文结合实际工程案例,详细讲解两种常见微型LED灯珠——HELI2直角型2.1X0.6mm与标准SMD-2.0X1.2m...

- 汽车级贴片电容哪家专业?深度解析行业领先品牌与选型要点 如何挑选真正专业的汽车级贴片电容?关键看这几点随着汽车电子化程度不断提升,汽车级贴片电容在电源滤波、信号耦合、去耦稳压等环节发挥着不可替代的作用。面对众多供应商,如何判断哪家更专业?本文从技术标准、产...

- 与其他品牌相比,德国系统品牌在市场上的表现如何? 在当今市场上,德国系统品牌因其卓越的质量、精密的设计以及长久的使用寿命而享有盛誉。与同类产品中的其他国际品牌相比,如瑞典的宜家(IKEA)或美国的霍曼(Horman),德国系统品牌往往更注重产品的耐用性和功能性。例如,德...

- 1安铅保险丝直径约0.5至0.8毫米 铅保险丝的直径与所需通过的最大电流有关。一般来说,用于1安培电流的铅保险丝直径大约在0.5毫米到0.8毫米之间,但具体尺寸还需参照实际产品的规格表或制造商提供的数据。因为不同制造商可能有略微不同的设计标准和材料...

- 电阻精密度1%能代0.1%吗? 不能!其实,对于不是搞计量的不需要分的那么清楚,可以大体上认为高精密、高准确、低误差等是一个意思。但是,对于“精度”一词,可以分解成分解成三个要素: 1 、温度系数:温度变化是电阻的大敌,温度系数一...

- FGT数码3 1/2位真空压力开关:高精度与可靠性的工业解决方案 FGT数码3 1/2位真空压力开关是一种先进的设备,用于精确控制和监测真空环境下的压力变化。这种开关以其高精度和可靠性著称,在多种工业应用中发挥着重要作用。它能够提供3 1/2位数的显示精度,这意味着用户可以获取到非常...

- ‘光颉光颉’网络用语爆火背后:从品牌名到梗文化的演变 从企业名称到网络迷因:‘光颉光颉’的传播现象分析近年来,“光颉光颉”这一原本属于电子元器件品牌“光颉科技”的名称,意外成为中文互联网上的热门网络用语。它最初源于网友对品牌发音的戏仿,逐渐演变为一种带有...

- 车用音讯放大器与滤波电容的协同设计:提升车载音响系统性能的关键 车用音讯放大器与滤波电容的重要性在现代汽车音响系统中,音讯放大器是核心组件之一,负责将微弱的音频信号放大至足以驱动扬声器的水平。而滤波电容则在电源供应环节起着至关重要的作用,有效滤除电源中的杂波和噪声...

- SMD-2.0X1.2mm与SMD-1.6X0.8mm LED灯珠对比分析:选型指南与应用优势 LED灯珠尺寸解析:SMD-2.0X1.2mm vs SMD-1.6X0.8mm在现代照明与显示技术中,LED灯珠的封装尺寸直接影响产品的性能、功耗与应用场景。其中,SMD-2.0X1.2mm和SMD-1.6X0.8mm是目前市场上广泛应用的两种小型化LED芯片型号。本文将从物理参数、电...