高速电路设计中时钟缓冲器的选型策略

随着集成电路工作频率不断攀升,时钟信号的延迟与抖动问题日益突出。正确选择零延迟缓冲器或低延迟时钟缓冲器,是确保系统稳定运行的关键环节。

一、影响选型的关键参数

1. 延迟(Latency): 指信号从输入到输出的时间差。零延迟缓冲器追求相位对齐,而低延迟缓冲器强调最小化物理延迟。

2. 抖动(Jitter): 包括周期抖动(Period Jitter)与相位抖动(Phase Jitter)。低延迟缓冲器通常具备更低的固有抖动。

3. 通道数量与扇出能力: 多路输出需求下,应选择支持高扇出(如1:8或1:16)的缓冲器,避免信号畸变。

二、典型应用案例分析

案例1:数据中心服务器主板

- 需求:多核处理器间时钟同步,要求相位一致。

- 解决方案:采用零延迟缓冲器,确保所有核心接收到同相位时钟信号。

案例2:5G基站射频前端

- 需求:低延迟、低抖动时钟分配至多个收发模块。

- 解决方案:选用低延迟时钟缓冲器,满足纳秒级响应要求。

三、设计注意事项

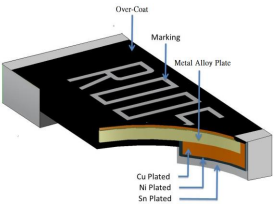

- 电源去耦: 使用旁路电容(如0.1μF + 10μF组合)减少电源噪声对时钟的影响。

- PCB布线: 采用等长走线、差分对布线,避免引入额外延迟。

- 温度稳定性: 优先选择具有宽温范围(-40°C ~ +105°C)的缓冲器,适应工业环境。

四、未来发展趋势

随着先进制程(如5nm、3nm)的发展,时钟缓冲器正朝着更高集成度、更低功耗方向演进。新型基于硅光子的时钟分布技术也正在探索中,有望在未来实现真正意义上的“零延迟”传输。